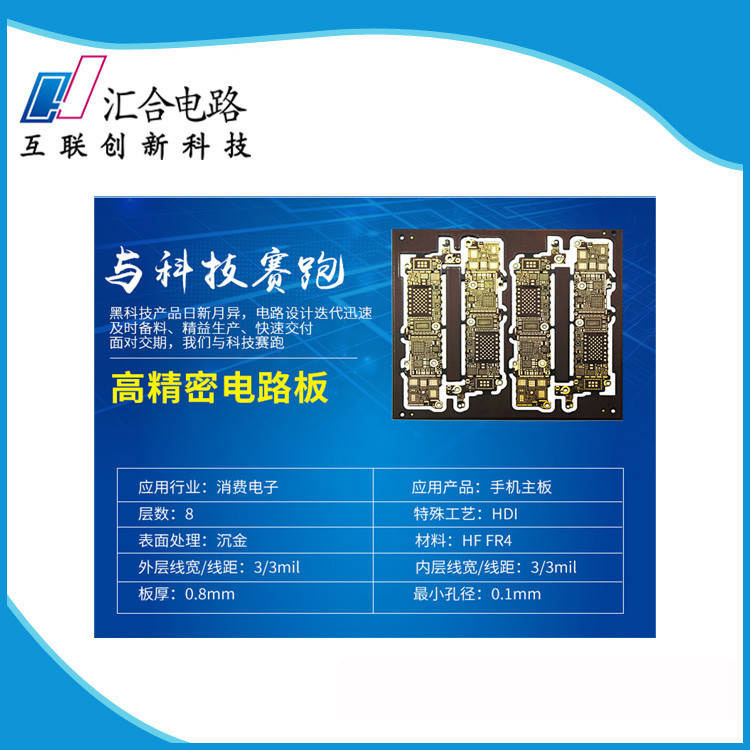

pcb多層線路板生產(chǎn)(深圳市匯合電路)pcb電路板產(chǎn)品包括2-28層板���、HDI板�、高TG厚銅板、軟硬結(jié)合板��、高頻板�����、混合介質(zhì)層壓板�、盲埋孔板、金屬基板和無鹵素板����。Pcb的應(yīng)用領(lǐng)域涉及廣泛,下面我們來了解下微控制器電路pcb的設(shè)計(jì)���。

微控制器電路PCB設(shè)計(jì)如下:

(1)合理分區(qū)���。微控制器電路PCB通常可分為模擬電路����、數(shù)字電路和功率驅(qū)動(dòng)三個(gè)區(qū)。要本著盡量控制噪聲源�、盡量減小噪聲的傳播與耦合、盡量減小噪聲的吸收這三大原則進(jìn)行PCB的設(shè)計(jì)和布線���。

(2)在元器件的布局方面�,應(yīng)該使相互有關(guān)的元件盡量放得靠近一些����。例如,時(shí)鐘發(fā)生器、晶振����、CPU的時(shí)鐘輸入端都易產(chǎn)生噪聲,在放置時(shí)應(yīng)把它們靠近些�����。對(duì)于那些易產(chǎn)生噪聲的器件�、小電流電路、大電流電路開關(guān)電路等�����,應(yīng)盡量使其遠(yuǎn)離微控制器的邏輯控制電路和存儲(chǔ)電路(ROM����、RAM),如果可能的話,可以將這些電路另外分成獨(dú)立小區(qū)進(jìn)行設(shè)計(jì)�,這樣有利于抗干擾,提高電路工作的可靠性�����。盡量不要使用1C插座��,要把1C直接焊在PCB上,以減少1C插座的分布參數(shù)影響���。

(3)在微控制器系統(tǒng)中,地線的種類有很多���,有系統(tǒng)地�����、屏蔽地�����、數(shù)字地���、模擬地等,地線是否布局合理��,將決定電路板的抗干擾能力���。在設(shè)計(jì)地線和接地點(diǎn)時(shí)�,應(yīng)該考慮以下問題���。

①數(shù)字地和模擬地要分開布線����,不能合用,要將它們各自的地線分別與相應(yīng)的電源地線相連��。Pcb多層電路板廠家一般在設(shè)計(jì)時(shí)���,模擬地線盡量加粗��,而且盡量加大引出端的接地面積�。一般來講�,對(duì)于輸入、輸出的模擬信號(hào)����,與微控制器電路之間最好通過光耦進(jìn)行隔離。

②在設(shè)計(jì)數(shù)字電路的PCB時(shí)��,其地線應(yīng)構(gòu)成閉環(huán)形式�,以提高電路的抗干擾能力。

③地線應(yīng)盡量粗�����。如果地線很細(xì)的話,則地線電阻將會(huì)較大���,會(huì)造成接地電位隨電流的變化而變化���,致使信號(hào)電平不穩(wěn)�,導(dǎo)致電路的抗r擾能力下降。在布線空間允許的情況下��,要保證主要地線的寬度至少為2?3mm,元件引腳上的接地線應(yīng)該在1.5mm左右��。

④要注意接地點(diǎn)的選擇��。當(dāng)PCB上的信號(hào)頻率低子1MHz時(shí)��,由于布線和元件之間的電磁感應(yīng)影響很小��,而接地電路形成的環(huán)流對(duì)干擾的影響較大����,所以要采用一點(diǎn)接地,使其不形成冋路�����。當(dāng)PCB上的信號(hào)頻率高于10MHz時(shí),由于布線的電感效應(yīng)明顯���,地線阻抗變得很大�����,此時(shí)接地電路形成的環(huán)流就不再是主要的問題了����,應(yīng)采用多點(diǎn)接地����,盡量降低地線阻抗。

(4)盡可能采用數(shù)字電路電源和模擬電路電源分別供電����。布置電源線時(shí),除了要根據(jù)電流的大小盡量加粗走線寬度外��,在布線時(shí)還應(yīng)使電源線���、地線的走線方向與數(shù)據(jù)線的走線方向—致���。在布線工作的最后��,要用地線將PCB的底層沒有走線的地方鋪滿���。上述這些方法都有助r增強(qiáng)電路的抗干擾能力。

(5)盡可能在微控制器����、ROM、RAM等關(guān)鍵芯片的電源輸入端安裝去耦電容器�����。實(shí)際上��,PCB走線、引腳連線和接線等都可能含有較大的電感效應(yīng)。大的電感可能會(huì)在Vo:走線上引起嚴(yán)重的開關(guān)噪聲尖峰����。防止Vex走線上開關(guān)噪聲尖峰的方法是在Vcc與電源地之間安放一個(gè)O.lpF的去耦電容器。如果PCB上使用的是表面貼裝元件����,可以用片狀電容器直接緊靠著芯片的Vcc引腳安裝。最好使用瓷片電容器����,這是因?yàn)檫@種電容器具有較低的靜電損耗(ESL)和高頻阻抗�,另外這種電容器在溫度和時(shí)間上的介質(zhì)穩(wěn)定性也很不錯(cuò)�。盡量不要使用鉭電容器,因?yàn)樵诟哳lK它的阻抗較高�。在安放去耦電容器時(shí)需要注意:在PCB的電源輸入端跨接10CVF左右的電解電容器時(shí),如果體積允許的話�,電容量大一些則更好;原則上每個(gè)集成電路芯片的旁邊都需要放置一個(gè)O.Ol^iF的瓷片電容器�,如果電路板的空隙太小而放置不下時(shí),可以每丨0個(gè)芯片左右放置一個(gè)1?10|jF的鉭電容器���。對(duì)于抗下擾能力弱�����、關(guān)斷時(shí)電流變化大的元件和RAM���、ROM等存儲(chǔ)元件,應(yīng)該在電源線(Vcc)和地線之間接入去耦電容器�。

(6)在能夠滿足系統(tǒng)要求的情況下,應(yīng)盡可能采用低的時(shí)鐘頻率��。時(shí)鐘產(chǎn)生器要盡量靠近用到該時(shí)鐘的器件。石英晶體振蕩器外殼要接地�,時(shí)鐘線要盡量短,且不要引得到處都是����。石英振蕩器下面、噪聲敏感器件下面要加大地的面積而不應(yīng)該走其他信號(hào)線���。時(shí)鐘線要垂直于I/O線����,避免與I/O線平行����;時(shí)鐘線要遠(yuǎn)離I/O線���。

(7)應(yīng)把時(shí)鐘振蕩電路����、特殊高速邏輯電路部分用地線圈起來����。

(8)I/O驅(qū)動(dòng)器件、功率放大器件盡量靠近PCB的邊緣,靠近接插件�。

(9)微控制器不用的I/O端口要定義成輸出。從高噪聲區(qū)來的信號(hào)要加濾波���。繼電器線圈處要加放電二極管�����??梢杂么粋€(gè)電阻的辦法來軟化I/O線的跳變沿或提供一定的阻尼����。

(10)數(shù)據(jù)線的寬度應(yīng)盡可能寬,以減小阻抗�����。數(shù)據(jù)線的寬度至少不小于0.3mm (〗2mil)��,如果采用0.46?0.5mm (18?20mil)則更為理想���。對(duì)噪聲敏感的線不要與高速線��、大電流線平行����。

(11)當(dāng)PCB尺寸過大或信號(hào)線頻率過高時(shí),可能會(huì)使得走線上的延遲時(shí)間大于等于信號(hào)上升時(shí)間����,這時(shí)該走線要按傳輸線處理,要加終端匹配電阻���。

Pcb多層電路板廠家(匯合電路)擁有強(qiáng)大的技術(shù)開發(fā)團(tuán)隊(duì)�����,掌握著行業(yè)工藝技術(shù)�,擁有可靠的生產(chǎn)設(shè)備�、測(cè)試設(shè)備和功能齊全的理化實(shí)驗(yàn)室。以上就是微控制器電路pcb的設(shè)計(jì)布局了��,pcb的世界是微妙的��,還有太多信息量等著去挖掘�����。

相關(guān)閱讀:印制板注意事項(xiàng)——深圳電路板廠有話說

掃描匯合電路服務(wù)號(hào)�����,更多匯合趣事等你來了解:

匯合電路服務(wù)號(hào)

掃描匯合電路微信小程序����,獲取更多PCB資訊:

?