由于越來越多的ADC采用了差分輸入結構���,所以差分驅動器已成為ADC驅動必要的器件��。目前��,有眾多技術可以將寬頻帶雙運算放大器應用于差分ADC驅動器���。理論上���,差分結構可以消除二次諧波失真�����。實際上���,只有精心布局的pcb快速打樣能夠有效地抑制二次諧波失真。采用對稱設計�����,可以通過差分反相配置來使放大器獲得最好的轉換速率����。

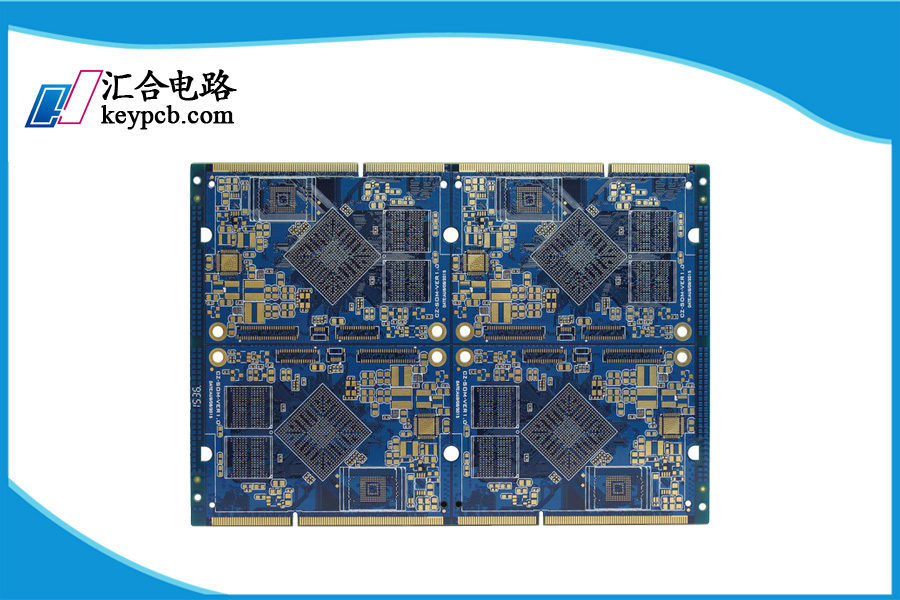

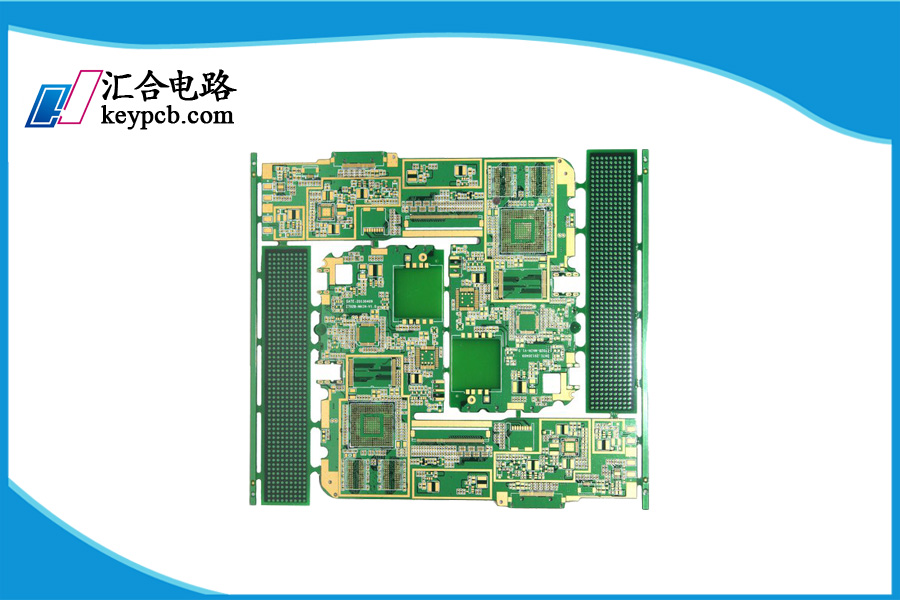

為了使差分結構對于二次諧波失真的消減能力達到最佳,必須對pcb快速打樣的板層數(shù)���、特征阻抗�、元件位置����、地線層���、對稱性、電源去耦合及其他許多方面進行優(yōu)化�����,這些在設計PCB時都需要被考慮到��。

pcb快速打樣采用對稱設計�,需要考慮元件對稱性和信號路徑對稱性。元件對稱性是指所有的板上元件都按照特定的模式排列��。信號路徑對稱性是指更注重的是信號路徑的對稱性而不是元件布局上的對稱砂��。

一個采用運算放大器OPA695構成的差分驅動器與ADS55OO ADC的接口電路���,考慮元件對稱性的pcb快速打樣設計。對稱中線被定義為穿過變壓器(Tin)中央的直線���。輸出電阻Routa和Route基于對稱中線等距分布���。盡管這種布局看上去使人賞心悅目,但仔細分析����,可以看到它仍然對放大器引腳輸出的信號路徑產生了一定的影響�����。例如���,在SOIC-8封裝的運算放大器中,輸出引腳通常在引腳端6,因此��,UA的引腳端6到中心的距離與UB的不同�。這種差異必須通過加長某一信號路徑的方式來補償。

相關閱讀:數(shù)字集成電路板制作模擬方法【匯合】